発表のポイント

◆ 生成AIなどによるAI推論のパラメータ数とAI計算に必要なメモリ容量の増加が進む中、データ記憶と演算を一体化することで、AI推論の低電力化が可能なアクセラレータ、ReRAM(抵抗変化型)で構成されるCiM(Computation-in-Memory)を多値記憶によりメモリ容量を増加しつつ、10年記憶を両立することに成功しました。

◆ CiMを構成するアナログReRAMを多値記憶により大容量化すると、パラメータ保持中にメモリ信頼性が劣化する問題があります。本研究では、メモリ信頼性の劣化に起因するAI推論時の積和演算の変化を補正する手法を提案し、多値記憶による大容量化を実現しつつ、10年間にわたる高いAI推論精度を達成しました。

◆ モビリティ・ロボティクス・ヘルスケア・モバイル応用等では、AI半導体の低電力化が急務です。本技術によりこれらのエッジ応用において低電力エッジAI半導体CiMの利用が拡大し、GX(グリーントランスフォーメーション)へ貢献することが期待されます。

40nm TaOXベースの多値アナログReRAMテストチップ

概要

東京大学大学院工学系研究科の竹内健 教授、松井千尋 特任准教授らによる研究グループはヌヴォトンテクノロジージャパン株式会社と共同で、モビリティ・ロボティクス・ヘルスケア・モバイルなどエッジ機器におけるAI推論で期待される、低電力エッジAI半導体であるReRAM CiM の多値記憶による大容量化と10年記憶の両立に成功しました。CiMではメモリと演算器を一体化することで、従来の課題であるメモリのデータ移動に使われる電力を大幅に抑えられます。生成AIなどによりAI推論のパラメータ数とAI計算に必要なメモリ容量の増加が進む中、CiMに多値記憶を採用することによりメモリ容量を増加することが可能になります。

CiMを構成する抵抗変化型メモリ(ReRAM)を多値記憶により大容量化した際には、パラメータ保持中にメモリ信頼性が劣化する問題があります。本技術では、データ保持時間をモニタする回路を導入し(図1)、モニタしたデータ保持時間に基づいて、メモリ信頼性の劣化に起因するAI推論時の積和演算の変化を補正する手法を提案しました。更に、メモリのエラーにロバストなAI計算の活性化関数を採用することで、多値記憶による大容量化を実現しつつ、10年間にわたる高いAI推論精度を達成しました。

本研究成果は、2025年9月11日にドイツ ミュンヘンで開催されるIEEE European Solid-State Electronics Research Conference(ESSERC)にて口頭発表されました。

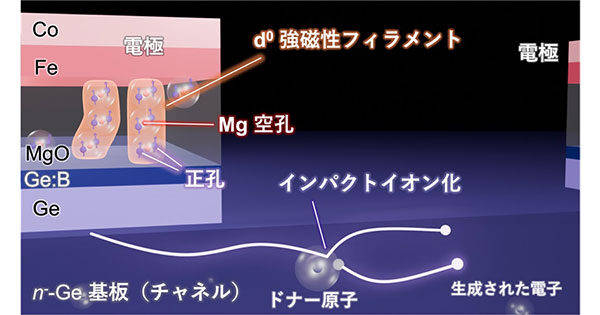

図1:提案する低電力・高信頼・多値記憶ReRAM CiM回路システム

発表内容

GPUなどAIの推論処理を実行する半導体に比べ、電力を1/10以下に抑えられると期待されるCiMが注目されています。従来のコンピュータでは、データ処理を行うプロセッサとデータを記憶するメモリの間のデータの移動が電力・速度のボトルネックとなっており、フォン・ノイマン・ボトルネックと呼ばれています。ReRAM CiMはアナログReRAM(抵抗変化型メモリ)で構成されるため、データ処理と記憶を一体化することでフォン・ノイマン・ボトルネックを解決すると期待されています。

一方、生成AIの発展に伴いニューラルネットワークは大規模化を続けており、そのパラメータ(重み)も増大しています。これに対応するため、膨大なパラメータを記憶する大容量のメモリが求められています。CiMを構成するReRAMに2ビット以上を記憶する多値記憶を採用することで、CiMのメモリ容量を増加することが可能になります。しかし、多値記憶には、ReRAMメモリ中の伝導パスを構成する酸素欠陥の拡散により、10年といった長期動作中に、メモリのデータにエラーが生じるという問題があります。CiMを構成するReRAMのメモリエラーはニューラルネットワークのパラメータのエラーに相当し、AI推論で重要となる積和演算値(MACV)の変動、ひいてはAI推論の精度劣化につながります(図2)。

図2:多値アナログReRAMのデータ保持中の信頼性の劣化(高温での加速実験による実験結果)

および酸素欠陥(VO)拡散の物理モデル

本技術ではデータ保持時間をモニタする回路を導入し、モニタしたデータ保持時間に基づいて、メモリ信頼性の劣化に起因するAI推論時の積和演算の変化を補正する手法を提案しました。更に、メモリのエラーにロバストなAI計算の活性化関数(ELU)を採用することで積和演算の変化を精緻に補正することに成功しました(図3)。AIのパラメータのうち上位ビットを1ビット記憶の2値メモリセル、下位ビットを多値メモリセルに記憶するハイブリッド構造を採用することで、従来の2値記憶のCiMに比べて、多値記憶による大容量化を実現しつつ、10年間にわたる高いAI推論精度を達成しました(図4)。

図3:本技術によるAIの積和演算値(MACV)補正の実験結果

図4:本技術によるAIの推論時間の実験結果。高温で加速実験を行い10年間動作を確認。

本技術によりCiMの多値化によるメモリ容量の大容量化と10年間の高信頼性が両立することが可能になり、モビリティ・ロボティクス・ヘルスケア・モバイル応用等への低電力エッジAI半導体CiMの利用が拡大すると期待されます。そしてエッジAIの低電力化により、GX(グリーントランスフォーメーション)へ貢献することが期待されます。

〇関連情報:

「世界最高水準の低消費電力化を実現するAI半導体向け「脳型情報処理回路」を開発」(2018/6/18、NEDO ニュースリリース)

https://www.nedo.go.jp/news/press/AA5_100977.html

発表者・研究者等情報

東京大学大学院工学系研究科

附属システムデザイン研究センター

竹内 健 教授

兼:電気系工学専攻 教授

電気系工学専攻

松井 千尋 特任准教授

三澤 奈央子 学術専門職員

平田 佑亮 研究当時:修士課程

山内 堅心 研究当時:修士課程

学会情報

学会名:European Solid-State Electronics Research Conference(ESSERC)

会 期:2025年9月8日~11日(中央ヨーロッパ夏時間)

題 名:Adaptive Oxygen Vacancy Diffusion Compensation in MLC Intermediate States for over 10-year Data-retention of TaOx ReRAM Analog CiM Array

著者名:Yusuke Hirata*, Kenshin Yamauchi, Naoko Misawa, Chihiro Matsui, Ken Takeuchi

URL:https://www.esserc2025.org

研究助成

本研究は国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の助成業務(JPNP23015)の支援により実施されました。

プレスリリース本文:PDFファイル

おすすめ記事