1.発表者:

北原 暁(東京大学 大学院工学系研究科 物理工学専攻 博士課程学生(研究当時)

井川 光弘(東京大学 大学院工学系研究科 物理工学専攻 特任研究員)

松岡 悟志(東京大学 大学院工学系研究科 物理工学専攻 助教)

荒井 俊人(東京大学 大学院工学系研究科 物理工学専攻 講師)

長谷川 達生(東京大学 大学院工学系研究科 物理工学専攻 教授)

2.発表のポイント:

◆高撥液なフッ素樹脂層上に高均質に塗布製膜し内因的/外因的トラップの密度を極小化

◆高急峻なスイッチング特性・高いバイアス耐性・低電圧安定駆動を同時に実現

◆実用的な逆コプラナー型素子構造により高精細配線と統合した印刷製造技術を確立

3.発表概要:

東京大学大学院工学系研究科物理工学専攻の北原 暁 大学院生(研究当時)、井川 光弘 特任研究員、松岡 悟志 助教、荒井 俊人 講師、長谷川 達生 教授らの研究グループは、ポリマー半導体(注1)による薄膜トランジスタ(TFT)(注2)のスイッチングの鋭さと安定性を決定づける要因を解明し、これをもとに従来にない高急峻なスイッチング動作・高いバイアス耐性・低電圧駆動を同時に示す、実用的な塗布型TFTの構築に成功しました。

ポリマー半導体は、優れた加工性や堅牢性により、フレキシブルエレクトロニクスの実現に向けた有望材料として期待されています。しかし、ポリマー半導体を用いた薄膜トランジスタ(TFT)は、急峻で安定したスイッチング動作を得ることが難しく、それら特性の改善が課題となっていました。本研究では、キャリアの動きを阻害しスイッチング特性を劣化させるトラップ(注3)が、ポリマー半導体層内部や半導体-絶縁層界面近傍に潜むことをつきとめ、その発生を抑え込む技術を開発しました。これにより、高精細な電極配線印刷技術と統合した実用性の高い逆コプラナー型(注4)デバイス構造において、従来にないきわめて高急峻なスイッチングと、高いバイアス耐性による安定した低電圧駆動を示す塗布型TFTの開発に成功しました。

本研究成果は、2021年10月12日(中央ヨーロッパ夏時間)にドイツ科学誌 Advanced Functional Materialsに掲載されました。

4.発表内容:

① 研究の背景

有機半導体は、シリコンなどの既存の無機半導体には真似のできない、軽い・柔らかい・塗布できるという特長を有することから、電子デバイスの軽量・ウェアラブル化や、デバイス製造における省資源・省エネルギー化を可能にする次世代半導体として期待されています。

有機半導体には、ポリマー系と低分子系の2系統があります。ポリマー半導体は、優れた加工性や堅牢性により、フレキシブルエレクトロニクスを実現するための有望材料として期待されています。しかし、高性能化が近年大きく進む低分子系半導体と比べて、ポリマー半導体を用いたTFTは急峻で安定したスイッチング動作を得ることが難しく、そのスイッチング動作には10V以上の電圧印加が必要となるなど、低電圧・低消費電力駆動を実現することが課題となっていました。

② 研究の経緯

常温・常圧下における塗布により、軽量でフレキシブルな電子デバイスを製造するプリンテッドエレクトロニクス技術の研究開発の一環として、当研究グループでは、塗布型半導体の材料高度化と、これらを用いたTFTの高性能化に取り組んでいます。塗布型半導体として、高性能化が進む低分子系半導体に加えて、性能を示す指標である電界効果移動度は劣るものの、加工性や堅牢性に優れたポリマー半導体を高度化する研究を進めています。

低分子系半導体を用いた塗布型TFTでは、最近、理論限界に迫る超高急峻なスイッチング動作(SS値(注5)が平均で67ミリボルト)を得られることが明らかになりました。そこでは、高い層状結晶性(注6)を示す低分子系半導体と、撥液性(注7)の高いフッ素樹脂からなるゲート絶縁層(注8)を組み合わせることにより、スイッチング動作が鈍る原因となるトラップの発生を抑え込むことができました。しかし、ポリマー半導体は分子構造がより複雑で乱れが生じやすく、トラップ抑制にはより詳細な検討が必要となっていました。

今回、ポリマー半導体TFTにおいて急峻で安定したスイッチング動作を実現するため、高撥液なゲート絶縁層の利用に加えて、ポリマー半導体と電極の種類や膜質、およびこれらを組み合わせたデバイス構造について、徹底した比較検討を行いました。これによりポリマー半導体層の内外に潜むトラップを特定し、その発生を最小化するデバイス技術を開発しました。結果、ポリマー半導体として例外的に高急峻でバイアス印加による変化の見られない高安定なスイッチング動作を示すポリマー半導体TFTの構築に成功しました。

③ 研究内容

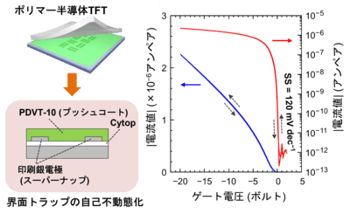

図1に、開発したポリマー半導体TFTのデバイス構造と、得られたスイッチング特性の一例を示します。SS値は最小で120ミリボルト(平均で126ミリボルト)で、低容量(注9)のゲート絶縁層を用いたポリマー半導体TFTとしては最も急峻性に優れたスイッチング動作が確認されました。デバイスの構成要素として、撥液性がきわめて高いアモルファス全フッ素化樹脂であるCytopをゲート絶縁層とし、電極には高精細電極配線パターン印刷技術(スーパーナップ法(注10))により形成した印刷銀電極を用いました。またポリマー半導体層は、高撥液ゲート絶縁層上に高速・高均質に一括製膜できるプッシュコート法(注11)により作製したものを用いました。ある種のポリマー半導体に、これらの要素材料と製膜手法を組み合わせて構築した逆コプラナー型TFTにおいて、最も優れたスイッチング動作が得られることを確認しました。

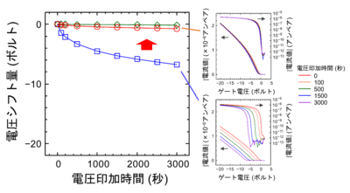

図2に、高急峻なスイッチング動作が得られたTFTについて、-20V以上のゲート電圧を一定時間印加した後のスイッチング特性が変化する様子を測定した結果を示します。特にこの結果から、ゲート電圧印加に対するバイアス耐性は、用いるゲート絶縁層の種類に大きく依存することが明らかになりました。高撥液なCytopをゲート絶縁層として用いた場合は、スイッチングに必要なゲート電圧が全く変化しない安定したスイッチング動作が得られています。その一方、表面が親液性のゲート絶縁層を用いた場合は、ゲート電圧印加とともにスイッチングに必要なゲート電圧が徐々に大きくなる傾向が観測されました。さらに後者の場合は、電極-半導体間のコンタクト抵抗も増大する傾向が見られました。

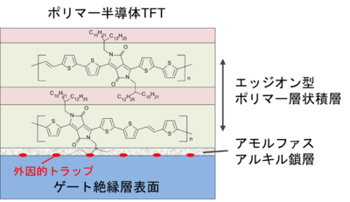

最も優れたスイッチング特性は、ポリマー主鎖が電子供与部位と電子受容部位が交互に連結してできたドナー・アクセプター型ポリマー半導体の一種であるPDVT-10を用いた場合に得られました。図3に、ゲート絶縁層上に形成された半導体層構造を模式的に示します。プッシュコート法を用いてPDVT-10による高均質・高秩序な半導体層を形成した場合は、ゲート絶縁層を変えるとバイアス耐性は影響を受ける(図2)ものの、高急峻なスイッチング動作は変わらず得られることが分かりました。一方、ポリマー半導体の種類を変えると、同一のデバイス構造・製膜手法であっても、スイッチング動作の様子は異なる挙動を示すことが分かりました。例えば、最も典型的なポリマー半導体であるP3HTを用いた場合は、高撥液なゲート絶縁層を用いた場合であってもSS値は400 ミリボルト程度にとどまり、かつ親液性のゲート絶縁層を用いるとSS値はさらに悪化する傾向が見られました。

これらの実験結果から、ポリマー半導体・PDVT-10のスイッチング動作を妨げるトラップには、スイッチングの急峻性に影響する内因的トラップと、バイアス耐性に影響する外因的トラップの2種類があることが推論されました。内因的トラップは半導体層内で発生し、高均質・高秩序な製膜によって発生を抑え込むことができます。これに対し、外因的トラップはゲート絶縁層との界面近傍で発生し、高撥液なゲート絶縁層を用いることにより抑え込めると考えられます。このような2種類のトラップが見られた理由は、PDVT-10の主鎖を構成するπ電子骨格(注12)どうしが高い秩序のもと配列しキャリア輸送層を形成しているのに対し、側鎖である分岐アルキル基は秩序化せずにアモルファス層を形成しているためと考えられます。不活性なアモルファス性のアルキル鎖層は、ゲート絶縁層との界面でトラップの原因となる極性基やイオン種を不動態化し(図3)、スイッチングを担う半導体層内でのキャリア輸送を保護する役割を担うことで、高急峻なスイッチング動作が実現したものと考えられます。

④ 今後の予定

本研究で開発したポリマー半導体TFTは、従来にない急峻で安定なスイッチング動作を示し、プリンテッドエレクトロニクスの革新技術になると期待できます。特にポリマー半導体の界面トラップを自己不動態化する分子機構の解明により、TFTの各構成部材の設計指針の確立とさらなるデバイス高性能化の進展が期待されます。またこれらポリマー半導体と高精細配線印刷技術の統合をより高度化し、軽量・ウェアラブルなデバイス応用に向けた全印刷化技術の開発を進めていく計画です。

本研究は、科学技術振興機構(JST)戦略的創造研究推進事業CREST「実験・計算・データ科学融合による塗布型電子材料の開発」(研究代表者:長谷川 達生、JPMJCR18J2)、JST研究成果最適展開支援プログラムA-STEP(JPMJTR202N)、JSPS科研費基盤研究(A)(18H03875)、JSPS科研費若手研究(19K15432)、JSPS科研費基盤研究(B)(19H02579)、JSPS科研費特別研究員奨励費(20J10479)および東京大学大学院工学系研究科リーダー博士人材育成基金特別助成プログラムLDPPによる支援を受けて行いました。

5.発表雑誌:

雑誌名:Advanced Functional Materials(オンライン版:10月12日)

論文タイトル:Approaching Trap-Minimized Polymer Thin-Film Transistors

著者:Gyo Kitahara*, Mitsuhiro Ikawa, Satoshi Matsuoka, Shunto Arai, Tatsuo Hasegawa*

DOI番号:10.1002/adfm.202105933

アブストラクトURL:https://doi.org/10.1002/adfm.202105933

6.用語解説:

(注1)ポリマー半導体

炭素・水素・酸素などから構成される有機半導体には、低分子系とポリマー系の2系統の材料がある。これらは溶液法により常温・常圧下での塗布により製膜できるという特長を有し、電子デバイスの軽量・ウェアラブル化や、デバイス製造における省資源・省エネルギー化を可能にする次世代半導体として期待されている。本研究ではポリマー半導体として、P3HT(ポリ (3-ヘキシルチオフェン-2,5-ジイル))と、PDVT-10(ポリ[2,5-ビス(アルキル)ピロロ[3,4-c]ピロール-1,4(2H,5H)-ジオン-alt-5,5'-ジ(チオフェン-2-イル)-2,2'-(E)-2-(2-(チオフェン-2-イル)ビニル)チオフェン])を用いた。

(注2)薄膜トランジスタ(TFT)

基板・電極・絶縁層・半導体を積層して作製される、電流のオンオフを電圧の切り替えにより制御する基礎的なスイッチング素子。ディスプレイの画素制御回路などに用いられる。

(注3)トラップ

トランジスタで電流が流れる経路中に存在し、電流を担う成分(電荷)を捕捉するエネルギー的な落とし穴のこと。半導体膜中や半導体・絶縁層の界面の欠陥に起因して生じうる。トラップの存在はスイッチング鋭さやデバイスの駆動安定性を損なうとされており、トラップのない電流経路を確保することがデバイスの信頼性確保に求められる。

(注4)逆コプラナー型

TFTは、構成要素である電極・絶縁層・半導体を積層して作製されるが、その積層順番に応じて4種類の名称がつけられている。下から電極・絶縁層・電極・半導体の順で積層されたTFTを逆コプラナー型と呼ぶ。一方、下から電極・半導体・絶縁層・電極の順で積層されたTFTをスタガー型と呼ぶ。このほか、半導体上に電極を形成するコプラナー型・逆スタガー型という構造がある。逆コプラナー・スタガー型は、半導体層直下の電極に対して、高精細配線プロセスが適用できるため(半導体層へのダメージを気にしなくてよい)、コプラナー型・逆スタガー型と比べてより実用的であると一般的には考えられている。

(注5)SS値

Subthreshold Swing(サブスレッショルド・スイング)値の略。電流値が立ち上がる領域において、電流値の1桁増大に必要な電圧値を表す(単位はボルト、厳密にはボルト/桁と書く)。スイッチング領域において電流は、電荷の密度勾配に起因した拡散流によって担われ、室温での理論最小値は60ミリボルトであることが導かれる。

(注6)層状結晶性

有機半導体を構成する分子が棒状である場合、棒状分子の側面どうしで働く分子間力は、棒状分子の先端どうしで働く分子間力と比べて、相対的に強くなる。したがって、棒状分子は側面どうしで集まりやすく、先端どうしで集まりにくくなる。これにより、二次元的に薄く広がった層状(シート状)の結晶(分子が規則正しく並んだ集合体)が得られやすくなる。このような結晶成長の性質を、層状結晶性と呼ぶ。

(注7)撥液性

ある基板表面に液滴を上からたらしたとき、液滴が丸まるような表面を「撥液性」、濡れ広がるような表面を「親液性」という。撥液性のもののうち、特によく液滴を弾くものを高撥液と呼び、フッ素樹脂は典型的な例である。液滴が水の場合は、「撥水性」「親水性」と呼ばれる。

(注8)ゲート絶縁層

電界効果トランジスタデバイスにおける部材の一つ。半導体に対して絶縁層越しに電圧を印加すると、絶縁層・半導体界面に電荷が誘起され、これがデバイス中を流れることで電流が流れる。絶縁層表面の性質はデバイス特性に大きく影響を与えることが知られており、例えば電気的・化学的に不安定な表面は電荷を捕捉しやすい(=トラップを形成しやすい)ため、デバイス駆動電圧の増大や駆動安定性の劣化を引き起こしうると考えられている。一方、高撥液などで安定な表面を有する絶縁層は、デバイス特性向上に有効とされる。

(注9)低容量

容量とは、ゲート絶縁層の静電容量のことであり、この値が大きいほど急峻なスイッチングが得られる(注5で述べたSS値は小さくなる)。有機トランジスタの標準としては例えば、シリコン熱酸化膜絶縁層(厚み100ナノメートル)の35ナノファラド/平方センチメートルがよく用いられる。本研究では25ナノファラド/平方センチメートルの静電容量を用いている。

(注10)スーパーナップ法

正式名は、SuPR-NaP法(Surface Photoreactive Nano-metal Printing)。フッ素樹脂表面に、真空紫外光(VUVと呼ばれる、高エネルギーの光)をパターン照射し、その上から銀インクを滴下・ブレード掃引することで電極を印刷形成できる手法。特殊な銀インクにより銀ナノ粒子が活性化した表面上に化学吸着する仕組みを用いることで、一般的な印刷法では到達できない1マイクロメートル以下の解像度の導電パターンの形成が可能になった。また本手法では通電(金属微粒子の焼成)のための高温処理(>100℃)も不要である。

参考1:超微細回路を簡便・高速・大面積に印刷できる新原理の印刷技術を開発

https://www.aist.go.jp/aist_j/press_release/pr2016/pr20160420/pr20160420.html

参考2:超高精細な印刷はなぜできる?

https://www.aist.go.jp/aist_j/press_release/pr2018/pr20180417/pr20180417.html

(注11)プッシュコート法

ポリマー半導体の塗布製膜手法の一つであり、高撥液絶縁層上へ半導体塗布製膜ができる数少ない手法である。塗布時は、半導体溶液を基板に滴下し、PDMSと呼ばれるシリコーンゴムで溶液を薄く押し広げる。毛管力を用いて溶液が薄く広がった状態を維持することで、溶剤のみがPDMSに吸収されて乾燥が進み、ポリマー半導体の固体膜が成長する。PDMSを基板から剥離することで、基板上にポリマー半導体膜を得ることができる。

参考:液体を強くはじく表面に半導体を塗布する新しい製膜技術

https://www.aist.go.jp/aist_j/press_release/pr2012/pr20121031/pr20121031.html

(注12)π電子骨格

二つの炭素原子などが多重結合(二重あるいは三重)を形成するとき、二原子間の電子軌道の重なりで形成されるσ(シグマ)結合に加え、σ結合面と垂直方向な電子軌道の重なりによるπ(パイ)結合が形成される。π結合に関わる電子をπ電子と呼ぶ。単結合と多重結合が交互に現れる系(共役系と呼ぶ)では、π電子が分子面全体に広がることで分子全体のエネルギーが安定化しており、こうした共役系を有する分子骨格をπ電子骨格と呼ぶ。

7.添付資料:

図1 ポリマー半導体TFTにおける高急峻なスイッチング動作の実現

左:ポリマー半導体TFTの作製工程(プッシュコート法)の模式図と、TFTの断面図。ゲート絶縁層であるCytop層上に印刷銀電極を配し、その上にポリマー半導体層を形成している。右:ドレイン電圧を2ボルトに固定して測ったTFT伝達特性。スイッチング時、電流値を10倍にするのに必要な電圧値(SS値)は120ミリボルト程度である。

図2 ポリマー半導体TFTにおける高いバイアス耐性の実現

左:電圧バイアス印加に対して、TFT伝達特性がどの程度変化するか(=電圧シフト量)を示した。電圧印加に対して、シフト量が0のままであれば安定なTFTと言える。○および◇は、高撥液Cytop絶縁層上にポリマー半導体を製膜したTFT。□は、シリコン酸化膜絶縁層上にポリマー半導体を製膜したTFT。同じ電界強度になるように、○と◇は-24V、□は-20Vの電圧バイアスを印加した。右:TFT伝達特性の電圧印加に対する挙動の比較。高撥液Cytop(上段)では高い駆動安定性が得られている一方、シリコン熱酸化膜(下段)では特性が電圧方向に平行移動シフトしている。

図3 ポリマー半導体界面のトラップ不動態化

ポリマー半導体PDVT-10の主鎖は、π電子骨格面を基板に対して垂直に立つように(エッジオン型)配列し、π電子骨格面どうしの配列秩序により優れた特性を示すキャリア輸送層を形成する。これに対し、側鎖である分岐アルキル基は秩序化せずにアモルファス層を形成し、ゲート絶縁層との界面でトラップの原因となる極性基やイオン種を不動態化していると考えられる。

プレスリリース本文:PDFファイル

Advanced Functional Materials:https://onlinelibrary.wiley.com/doi/10.1002/adfm.202105933

科学技術振興機構:https://www.jst.go.jp/pr/announce/20211012/index.html

日本経済新聞:https://www.nikkei.com/article/DGXLRSP619308_R11C21A0000000/

おすすめ記事

本件に関連する記事はこちら