発表のポイント

◆ カスケード型アーキテクチャで安定した雑音低減を達成する新方式を開発。

◆ 従来技術では必須の補正を必要とせずに、低ジッタ・低スプリアスを同時に達成。

◆ 高速無線通信に必要不可欠な低雑音の周波数シンセサイザ技術として、次世代無線通信規格への応用が期待される。

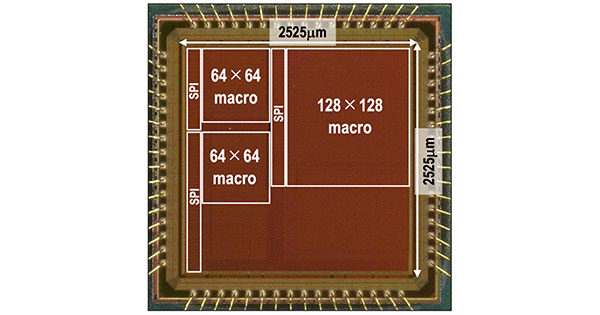

開発した新方式位相同期回路の65nmプロセスでの試作品写真

開発した新方式位相同期回路の65nmプロセスでの試作品写真

発表概要

東京大学大学院工学系研究科の飯塚 哲也 教授と、張 浩明 大学院生らによる研究グループは、低ジッタ(注1)と低スプリアス(注2)を同時に実現する位相同期回路(PLL:Phase-Locked Loop)(注3)の新方式を開発しました。

無線通信機などで広く用いられる分数分周PLL(注4)では、回路構成上生じる量子化雑音(注5)による雑音性能の劣化が問題となり、これを抑制する手法が数多く提案されてきました。多くの既存技術では、その量子化雑音を特定の回路技術により打ち消す方式を採用していますが、回路性能の補正が必要となりPLLのロック時間が長くなるという欠点がありました。

今回の研究では、二段のPLLを使用したカスケード構造において、二つのマルチモジュラス分周器(MMD:Multi-Modulus Divider)(注6)を用いた量子化雑音キャンセル手法と、初段の発振回路(注7)の雑音を低減するフィードフォワード型雑音キャンセル手法を適用した新たな回路構成により、補正不要の低雑音分数分周PLLを実現しました(図1)。開発したPLLは65ナノメートル(nm、1nmは10億分の1メートル) CMOS(相補性金属酸化膜半導体)プロセスで試作され、157フェムト秒(fs、1fsは1000兆分の1秒)のジッタ性能と–73dBcのスプリアス性能を実証し、出力周波数や分周比の設定に依らず安定した低雑音性能を実現しました。このPLLは、高速無線通信に必要不可欠な低雑音の周波数シンセサイザ技術として、Beyond 5Gや6Gなどの次世代無線通信規格への応用が期待されます。これにより、高速・低遅延といった通信性能のさらなる高度化に加え、高信頼性やエネルギー効率の向上などを通じて新たな社会的価値の創造につながります。

本研究成果は、2026年2月18日(米国太平洋時間)に、半導体集積回路分野の国際会議であるInternational Solid-State Circuits Conference(ISSCC)にて口頭発表されます。

図1:開発した新方式位相同期回路のブロック図

図1:開発した新方式位相同期回路のブロック図

二つのMMDによる量子化雑音キャンセル手法とフィードフォワード型雑音キャンセル手法によって補正が不要でありながら低ジッタと低スプリアスを同時に実現。

発表内容

<研究の背景>

Beyond 5Gや6Gといった次世代無線通信規格では、高い通信速度に加えて、低遅延や高い電力効率も強く求められています。限られた周波数資源の中で高速通信を実現するため、Wi-Fi 7などの規格では4K-QAMに代表される高次変調方式が採用されています。しかし、高次変調方式は信号品質に対する要求が高く、送受信機には極めて低雑音かつ高精度な回路技術が不可欠です。このような無線通信機やレーダーにおいて、位相同期回路(PLL)は、基準周波数信号を生成する主要な構成要素であり、その性能はシステム全体の通信品質に直結します。特に、より雑音の少ない基準信号を、低消費電力かつ短い整定時間で生成することが求められ、このことが、システムのスループットや省電力性能の向上につながります。このような背景から、より高性能なPLLの研究開発は、次世代無線通信機や高精度レーダーの実現に向けて世界的に活発に進められています。

<研究の内容>

PLLの位相雑音を低減する手法として、サンプリング位相検出器(SPD)を用いたサンプリングPLL(SPLL)が広く研究されています。SPLLでは、SPDの高いゲインにより、PLL帯域内の位相雑音を低く抑えることができ、低雑音の周波数出力を実現します。しかし、SPDが好ましい特性を示す入力の範囲は非常に狭く、通常は数十ピコ秒(ps、1psは1兆分の1秒)程度しかありません。一方、一般的な分数分周PLLでは位相検出器の入力に数百ピコ秒程度の量子化誤差が生じ、位相雑音やスプリアス特性が劣化してしまいます。この問題を解決するため、SPDの前段にデジタル時間変換器(DTC:Digital-to-Time Converter)(注8)を配置し、量子化雑音のキャンセルを行う手法が広く採用されています。しかしながら、DTCの持つ非線形性により、位相雑音やスプリアス性能の劣化を招く可能性があり、通常はその性能補正を複雑なデジタル信号処理によって行う事が必要不可欠です。その結果、補正の処理に必要な時間と合わせてPLLの出力静定時間が長くなってしまうという欠点がありました。

今回の研究で開発したPLLでは主に以下の二つの回路技術を適用することで、分数分周PLLにおいて補正を不要としながら低ジッタと低スプリアスを同時に実現することに成功しました。

(1)二つのMMDによる量子化雑音キャンセル手法

DTCを用いない量子化雑音キャンセル手法として、二段のカスケード型のPLLにおいて、共通のデルタシグマ変調器(DSM:Delta-Sigma Modulator)(注9)によって制御された二つのMMDを用いる事で、後段PLLに入る量子化雑音を、後段PLLの分周比Nに対して1/Nに低減できる技術を提案し採用しています。この量子化雑音の低減効果は回路性能の温度や電圧といった環境依存性や非線形性などの性質に影響されないため、補正不要の量子化雑音低減が可能になります。この技術を用いる事で、例えば3次のDSMで分周比Nが20、出力周波数が5GHzの場合、位相検出器に入力される量子化雑音は約800psから約40psまで低減されます。

(2)フィードフォワード型雑音キャンセル手法

二段カスケード構造のPLLでは、それぞれのPLLに一つずつの発振回路が必要となり、一般的に低雑音であるLC型発振回路(注10)を二つ用いると占有面積が大きくなることが懸念されます。面積低減のためにリング型発振回路(注11)を初段PLLに用いると、その雑音が全体の雑音性能を律速し、性能低下につながります。今回開発したPLLでは、初段の位相検出器の電圧出力を、後段のPLLの位相検出器出力にそのままフィードフォワードし加算することで、初段発振器の雑音をキャンセルする手法を提案し採用しています。これにより、初段発振回路には雑音は大きいが小面積であるリング型発振回路を採用でき、実装面積の削減が可能となります。また、雑音キャンセルのためには周波数設定に応じたフィードフォワード経路のゲイン調整が必要となりますが、今回開発したPLLでは、二つのPLLに共通の回路構造を持つSPDを用い、その位相検出器としてのゲインが入力周波数に応じて変化するという特長を活用することで、設定した分周比に依存せず、周波数設定に依らないロバストな雑音キャンセル手法を実現しました。

提案したPLL回路を65nm CMOSプロセスを用いて試作しました(図2)。実測評価により157fsのジッタ性能と–73dBcのスプリアス性能を実証し、出力周波数や分周比の設定に依らず安定した性能を確認しました。

<今後の展望>

本研究の成果を基盤として、さらに高性能かつ実用的な位相同期回路を実現すべく、新しいアーキテクチャや回路技術の開発を進めていきます。加えて、無線通信機などの実際のアプリケーションへの適用を視野に入れ、その有効性を検証していきます。

図2:試作チップ写真(左)と消費電力・チップ面積の内訳(右)

発表者・研究者等情報

東京大学 大学院工学系研究科 電気系工学専攻

飯塚 哲也 教授

張 浩明 博士課程

何 永隽 修士課程

朱 玉揚 博士課程

任 煥宇 修士課程

発表学会

学会名:International Solid-State Circuits Conference(ISSCC)

会 期:2026年2月15日〜19日(論文配布は2月13日、発表は2月18日8:25-8:50。いずれも米国太平洋時間。)

題 名:A 157fsrms-Jitter, −73dBc-Fractional-Spur, Calibration-Free Cascaded SPLL Employing Robust Feedforward Noise Cancellation and MMD-Based Quantization-Error Cancellation with a 60MHz Reference

著者名:Haoming Zhang, Yongjuan He, Yuyang Zhu, Huanyu Ren, and Tetsuya Iizuka*

研究助成

本研究成果は、主として、以下の事業・研究領域・研究課題によって得られました。

科学技術振興機構(JST)情報通信科学・イノベーション基盤創出(CRONOS)(課題番号:JPMJCS24K1)

領域名:川原領域

研究開発課題名:無線・光融合技術の確立による革新的無線通信システムの創出

研究代表者名:飯塚 哲也(東京大学 大学院工学系研究科 教授)

用語解説

(注1)ジッタ:信号の立ち上がりまたは立ち下りのタイミングが雑音によって揺らぐ現象。

(注2)スプリアス:意図する信号以外に出力に生じる不要な信号成分。基準電力とスプリアスの振幅値の比を相対値(単位はdBc)で表す。

(注3)位相同期回路(PLL:Phase-Locked Loop):外部の水晶発振器による基準周波数を元に、それを逓倍して所望の周波数の信号を得るための回路。

(注4)分数分周PLL:PLLには、整数分周型と分数分周型がある。整数分周型PLLでは基準信号に対して整数倍の周波数を出力するが、分数分周型では分数倍の任意の周波数の出力が可能である。無線通信やレーダー用途には、分数分周PLLが用いられる。

(注5)量子化雑音:細かい粒度の数値を粗い粒度の数値に丸め込むときに生じる誤差に起因する雑音のこと。分数分周PLLにおいては、整数の分周比を時分割で切り替えることによって実効的に分数の分周比を得るため、この雑音が生じる。

(注6)マルチモジュラス分周器(MMD:Multi-Modulus Divider):複数の分周比を切り替えられる分周器。

(注7)発振回路:PLLの制御対象であり、クロック信号や搬送波などに利用される一定の周波数の電気信号を生成するための回路。

(注8)デジタル時間変換器(DTC:Digital-to-Time Converter):デジタル制御信号によって遅延時間を制御する可変遅延回路。

(注9)デルタシグマ変調器(DSM:Delta-Sigma Modulator):分数分周PLLで用いられるデジタル変調器。整数の分周比を時間的に切り替えることで平均的に所望の分数分周比を実現する。量子化誤差を高周波領域に押し出し(ノイズシェイピング)、PLL帯域内の位相雑音を低減する役割を持つ。

(注10)LC型発振回路:発振回路のうち、出力周波数制御のためにインダクタンスと容量値によって決まる共振周波数を用いる方式。一般的に集積回路上で実装されるインダクタンスは占有面積が大きくなる傾向があり、LC型発振回路の占有面積も大きくなる傾向がある。

(注11)リング型発振回路:発振回路のうち、出力周波数制御をトランジスタによる論理ゲートの遅延の制御により行う方式。一般的にLC型と比較して小面積で実装でき周波数制御範囲が広いなどの長所があるが、同等の電力においてLC型よりも雑音が大きくなる傾向がある。

プレスリリース本文:PDFファイル

International Solid-State Circuits Conference(ISSCC):https://www.isscc.org/

おすすめ記事

開発コストを1/40に削減するAIプロセッサの新方式を開発 ―新規に必要なフォトマスクは1枚のみ、低コストと低電力動作を両立―

最も単純な「原子」ポジトロニウムをレーザー光によって1000万分の1秒で極低温にすることに成功 ―反粒子を含む原子の精密科学によって物理学の謎にせまる大きな第一歩―