発表のポイント

◆ シリコンチップ上で、これまでに利用されていなかった次元「光導波路多重」を用いて、光による行列-ベクトル乗算を実行する光プロセッサを実現。

◆ シンプルなシステム構成でありながら、大規模集積が可能なチップ構造を実証。

◆ 光導波路多重に加えて、従来の波長・モードの次元を組み合わせることで、AIに向けた超並列光行列演算回路の実現が期待される。

光導波路多重型シリコン光行列演算回路

概要

東京大学大学院工学系研究科電気系工学専攻の竹中 充 教授、唐 睿 特任助教(研究当時)、トープラサートポン カシディット 准教授、高木 信一 教授(研究当時)、及び産業技術総合研究所光電融合研究センター光電子集積デバイス研究チームの岡野 誠 上級主任研究員らの研究グループは、JST戦略的創造研究推進事業の支援のもと、次世代AIアクセラレータに向けて行列-ベクトル乗算を加速できる新しい光プロセッサを開発しました。

AI演算を加速する光プロセッサの研究は、現在世界的に大きな注目を集めています。従来の方式では、光の波長やモード(注1)などの自由度を利用して、光による行列-ベクトル乗算が実証されてきましたが、光信号の大きな減衰や信号同士の干渉などの問題により、大規模な光回路の実現には限界がありました。本研究では、複数の光導波路(注2)内の光信号を直接加算できる多ポート光検出器(注3)を世界で初めて開発・実装しました。これにより、これまでに利用されていなかった次元である「光導波路多重」の活用が可能となり、シンプルなチップ構成でありながら高いスケーラビリティ(拡張性)を持つ光行列演算回路の実証に成功しました。この成果は、光技術を活用した次世代AIプロセッサの実現に向けて、高速かつ省電力なハイブリッド演算アーキテクチャの確立に大きく貢献するものと期待されます。

本成果は、2025年6月4日(米国東部夏時間)に米国学術誌「Optica」のオンライン版にて公開されました。

発表内容

〈研究の背景〉

近年、生成AIや自動運転、ビッグデータ解析などの進展により、膨大な情報を高速かつ効率的に処理できる次世代の演算技術への期待が高まっています。特に、深層学習をはじめとするAI技術では、従来よりも桁違いに多くて複雑な演算が必要とされることから、行列-ベクトル乗算(MVM)が基本演算として頻繁に用いられています。行列という概念を導入することで高次の方程式を扱えるようになり、またベクトルは絶対量だけではなく向きについての情報も含む概念であることから、記述できる範囲が広がります。MVMの使用によって格段に処理できる情報が多くなる反面、その処理効率がAIシステム全体の性能を大きく左右します。従来、電子回路の大規模集積化によって計算性能は飛躍的に向上しており、半導体の集積度は約2年ごとに倍増する(ムーアの法則)と言われてきましたが、近年ではその勢いを失いつつあり、電子プロセッサの性能向上だけではAIのさらなる発展を支えきれない状況が見えていました。

このような背景のもと、光を用いて演算を行う光プロセッサが注目を集めています。光は電気に比べて伝送損失が小さく、高速かつ並列に信号を処理できるため、AI演算のボトルネックとなっているMVMを大幅に加速できると期待されています。これまでの光MVM回路では、波長多重(異なる色の光を使う)やモード多重(導波路内の異なる伝搬モードを使う)といった自由度が活用されてきました。しかし、光信号の大きな減衰や信号間の干渉などの問題があり、大規模な光回路への拡張には限界がありました。そのため、より高いスケーラビリティを持つ光MVM回路の実現が強く求められています。

〈研究の内容〉

本研究では、複数の入力ポートを有する多ポート光検出器により、異なる光信号を加算する構成を提案しました。これにより、複数の波長やモードを用いることなく、複数の光導波路内の光信号を一括して検出・加算することが可能となり、光導波路多重に基づく光MVMが実現されました。

本研究で実証した光MVM回路の構造を図1に示します。まず、光強度変調器アレイによって、ベクトルと行列の各要素に比例した光強度変調を行います。光信号は2回の強度変調を受けることで、ベクトルと行列要素の乗算が光のまま実行されます。変調された複数の光信号は多ポート光検出器によって受光され、合計の光パワーに比例した電流が出力されます。各光検出器の出力電流を読み取ることで、MVMの計算結果が得られます。光強度変調器は、マッハ・ツェンダー干渉計(MZI)、マイクロリング共振器、或いは相変化材料に基づいた減衰器などを使うことが可能です。今回の原理実証ではMZIを使用しました。多ポート光検出器は、Ge-on-Si(シリコン上にゲルマニウムを成長させた構造)の構造によって実現されており、入力された光はゲルマニウム内で吸収され、電流に変換されます。出力電流値は、各ポートからの入力光の合計パワーに比例するため、複数の光信号の加算が行われます。

図1:光導波路多重型シリコン光行列演算回路。

図2にシンガポールの半導体ファウンドリーAMF社で作製された16ポート光検出器の顕微鏡写真を示します。各入力ポートには、幅440 nm、厚さ220 nmのシリコン導波路が用いられています。コンパクトなデバイス面積と高応答速度を実現するために、入力ポート間の距離は徐々に300 nmまで縮められています。これにより、異なるポートに同じ波長の光が入力される際に光信号間の強い干渉が生じますが、それにもかかわらず加算処理がほとんど影響を受けないことが、シミュレーション及び実験により確認されました。

図2:作製された16ポート光検出器の顕微鏡写真。

図3に同じくAMF社で作製された4×4の行列を生成できる光回路の顕微鏡写真を示します。本光回路では、20個のMZIと4個の4ポート光検出器を使用しています。各MZIでは、薄膜の金属フィルムをヒーターとして用い、透過光の強度を電気的に制御しています。MZIアレイを制御してさまざまな行列を生成した結果を図4に示します。実測値と期待値を比較することで、高精度な動作ができることを確認できました。また、3層のニューラルネットワークを構築し、本光回路を用いてアイリス花の分類といった推論タスクを行いました。その結果を図5に示します。光回路でMVMを実行し、コンピュータでほかの演算を実行した結果、93.3%の高い正解率を実現できました。さらに、将来的な大規模光回路の使用を見据え、深層学習で広く用いられているFashion-MNISTの分類タスクに適用した結果、計算上で90.53%の高い正解率が得られました。

図3:(a)作製された4×4規模の光回路の顕微鏡写真。(b)実装された4×4光回路。

図4:光回路を制御してさまざまな行列を生成した結果。

図5:(a)アイリス花を識別用のニューラルネットワーク。(b)光回路を用いて推論を行った結果。

〈今後の展望〉

本研究では、これまでに利用されていなかった次元である「光導波路多重」を用いて、シンプルな構成で高いスケーラビリティを持つ光MVM回路の原理実証に成功しました。今後は、この技術を従来の波長・モード多重技術と組み合わせることで、より大規模な光回路の構築や、より高性能なAI処理への応用が期待されます。本研究は、光とシリコン集積回路の融合による新たな計算基盤の構築に貢献し、将来の高速かつ省電力な情報処理システムの実現に向けた重要な一歩となるものです。

発表者・研究者等情報

東京大学 大学院工学系研究科

竹中 充 教授

唐 睿 研究当時:特任助教

張 超 博士課程

トープラサートポン カシディット 准教授

高木 信一 研究当時:教授

産業技術総合研究所 光電融合研究センター

岡野 誠 上級主任研究員

論文情報

雑誌名:Optica

題 名:Waveguide-multiplexed photonic matrix-vector multiplication processor using multiport photodetectors

著者名:Rui Tang, Makoto Okano, Chao Zhang, Kasidit Toprasertpong,

Shinichi Takagi, and Mitsuru Takenaka*

DOI:10.1364/OPTICA.552023

URL:https://doi.org/10.1364/OPTICA.552023

研究助成

本研究は、科学技術振興機構(JST)戦略的創造研究推進事業 CREST(課題番号:JPMJCR2004)、日本学術振興会(JSPS)科学研究費助成事業若手研究(課題番号:22K14298)の支援により実施されました。

用語解説

(注1)モード

ここでは、光が伝搬する際の電磁場の空間分布の形を指します。

(注2)光導波路

光を特定の経路に沿って伝搬させるための構造です。

(注3)光検出器

光信号を電流信号に変換するデバイスです。

プレスリリース本文:PDFファイル

おすすめ記事

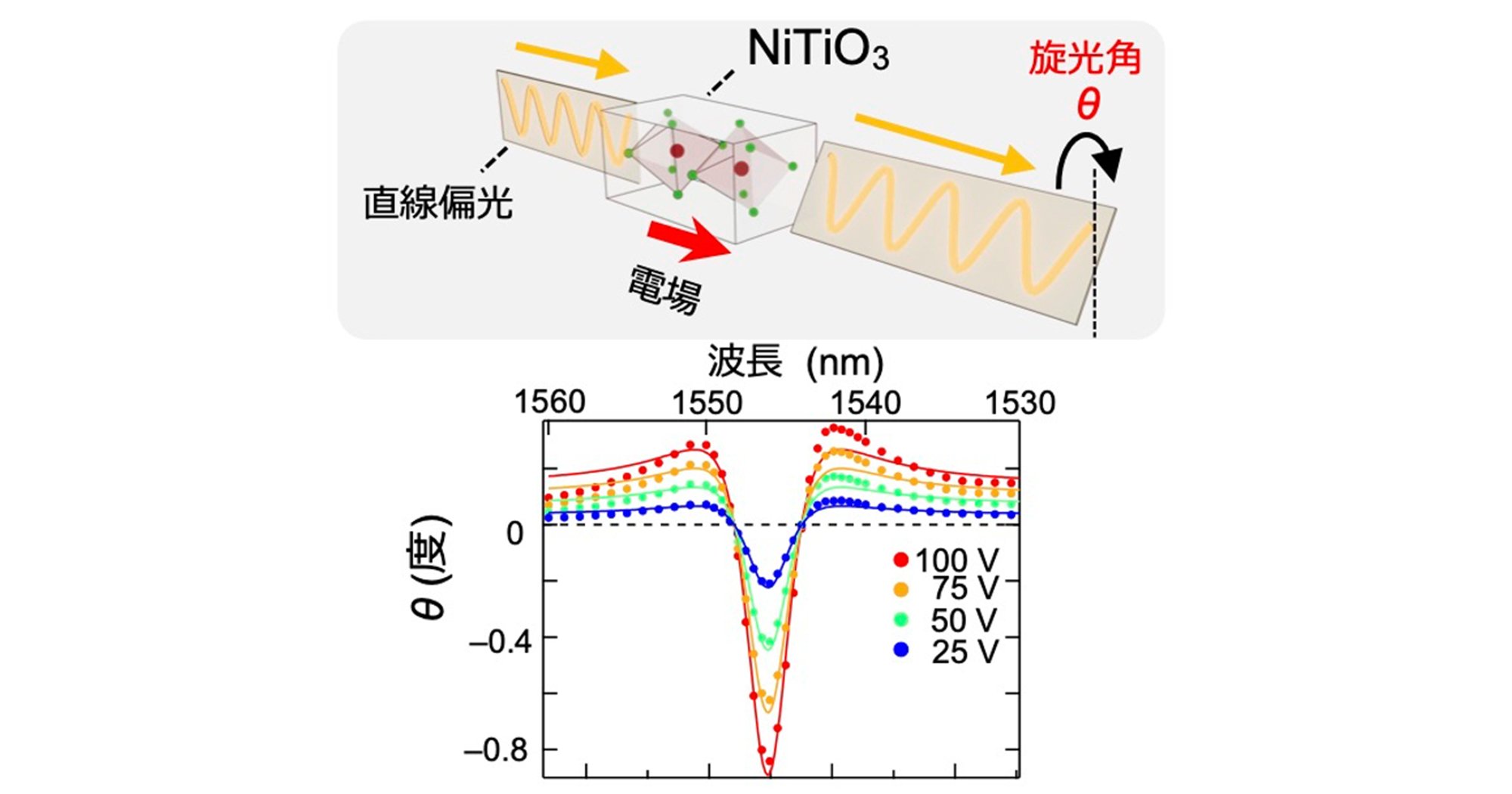

巨大な電場誘起旋光現象の観測 ―高効率な偏光制御デバイスの実現に向けて―

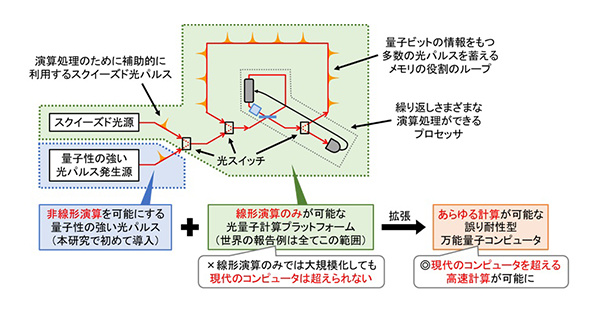

光量子計算プラットフォームに世界で初めて量子性の強い光パルスを導入 ―スパコンを超える光量子コンピュータへ突破口―