Share this

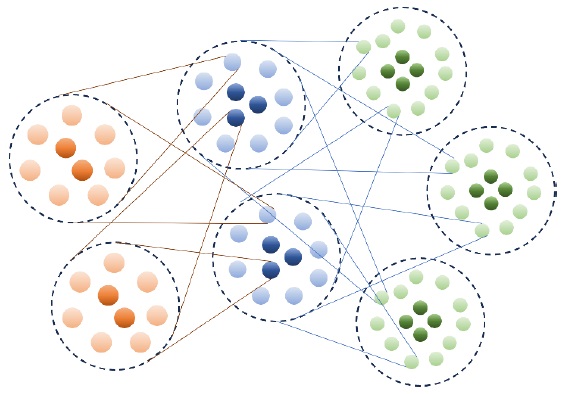

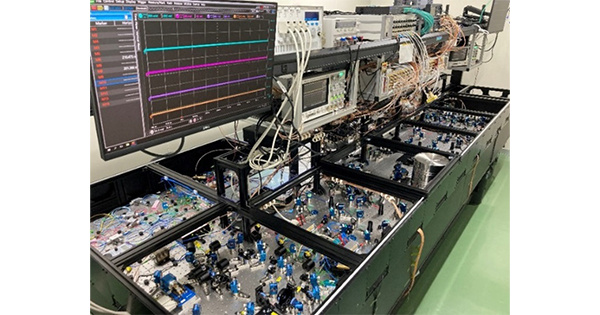

Fault-tolerant quantum computation (FTQC) enables reliable quantum computation by utilizing quantum error-correcting codes to encode logical qubits across multiple physical qubits in real quantum devices. However, this redundancy typically faces a dilemma: the conflict between hardware scale (the number of physical qubits) and computational speed. The research team at the University of Tokyo resolved this dilemma by introducing a hybrid fault-tolerant protocol that combines the strengths of two distinct quantum error-correcting codes. By assigning quantum low-density parity-check (QLDPC) codes for efficient information storage and concatenated codes for high-speed operations, the protocol achieves a significant reduction in the number of physical qubits while maintaining computational speeds comparable to the conventional methods.

To validate this protocol, the researchers developed a new analysis technique called partial circuit reduction. This method enables rigorous evaluation of error propagation by decomposing large-scale circuits into functional components, regardless of the specific quantum error-correcting code and its error-suppression mechanism. The study proves that the proposed protocol substantially reduces the scale of the required hardware while maintaining computational speed. This achievement provides a crucial theoretical foundation and design guidelines for accelerating the realization of fault-tolerant quantum computers.

A fault-tolerant quantum computer that achieves reduced hardware scale and high-speed computation using two types of quantum error-correcting codes

Journal: Nature Physics

Title: Fault-tolerant quantum computation with polylogarithmic time and constant space overheads

Authors: Shiro Tamiya*(corresponding author), Masato Koashi, Hayata Yamasaki